Вопрос:

Поэтому мне нужно получить синусовую форму. В случаях я написал значения оси x и y в диапазоне 2pi

как получить форму сигнала синуса в этом диапазоне?

module sinus1(in,clk,res,out); input clk,res; input [7:0]in; output reg [7:0]out; always @(posedge clk) if (res) case (in) 8’b00000000: out<=8’b10000000; 8’b00000001: out<=8’b10000011; 8’b00000010: out<=8’b10000110; 8’b00000011: out<=8’b10001001; 8’b00000100: out<=8’b10001100; 8’b00000101: out<=8’b10001111; 8’b00000110: out<=8’b10010010; … … … 8’b11111111: out<=8’b01111101; endcase else out<=8’b00000000; endmodule module testbench; reg clk,res; reg [7:0]in; sinus1 sinusoid(in,clk,res,out); always #5 clk=~clk initial begin clk=0;res=0; #5 res=1; #5000 $finish; end endmodule Лучший ответ:

Если вы хотите получить значения для каждого входа, вы должны подметать значения в своем тестовом банке, возможно, от 0 до 255. Вот ссылка, которая делает это на Eda Playground:

http://www.edaplayground.com/x/2bx

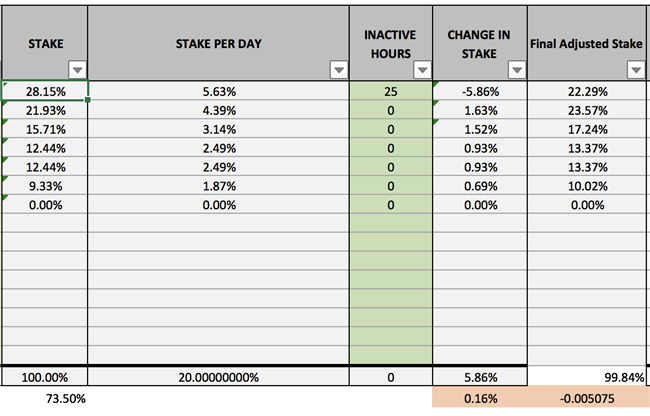

Вывод:

in=00000000, out = sin(in) = 10000000 in=00000001, out = sin(in) = 10000011 in=00000010, out = sin(in) = 10000110 in=00000011, out = sin(in) = 10001001 in=00000100, out = sin(in) = 10001100 in=00000101, out = sin(in) = 10001111 …